# NulPC® / NuDAQ® cPCI-7300A & PCI-7300A 80MB Ultra-High Speed 32-CH Digital I/O Boards User's Guide

©Copyright 2002 ADLINK Technology Inc. All Rights Reserved.

Manual Rev 2.31: 1 June, 2003

Part No.: 50-11106-101

The information in this document is subject to change without prior notice in order to improve reliability, design and function and does not represent a commitment on the part of the manufacturer.

In no event will the manufacturer be liable for direct, indirect, special, incidental, or consequential damages arising out of the use or inability to use the product or documentation, even if advised of the possibility of such damages.

This document contains proprietary information protected by copyright. All rights are reserved. No part of this manual may be reproduced by any mechanical, electronic, or other means in any form without prior written permission of the manufacturer.

#### **Trademarks**

NuDAQ<sup>®</sup>, NuIPC<sup>®</sup>, DAQBench<sup>®</sup> are registered trademarks of ADLINK Technology Inc.,

Other product names mentioned herein are used for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

# **Getting service from ADLINK**

Customer Satisfaction is the most important priority for ADLINK Tech Inc. If you need any help or service, please contact us.

| ADLINK Technology Inc. |                          |                                                              |                   |  |  |

|------------------------|--------------------------|--------------------------------------------------------------|-------------------|--|--|

| Web Site               | http://wv                | ww.adlinktech                                                | .com              |  |  |

| Sales &<br>Service     | Service@adlinktech.com   |                                                              |                   |  |  |

|                        | NuDAQ + USBDAQ           | nud                                                          | aq@adlinktech.com |  |  |

| Technical              | Automation               | automation@adlinktech.com                                    |                   |  |  |

| Support                | NuIPC                    | nuipc@adlinktech.com                                         |                   |  |  |

|                        | NuPRO / EBC              | nupro@adlinktech.com                                         |                   |  |  |

| TEL                    | +886-2-82265877          | FAX                                                          | +886-2-82265717   |  |  |

| Address                | 9F, No. 166, Jian Yi Roa | 9F, No. 166, Jian Yi Road, Chungho City, Taipei, 235 Taiwan. |                   |  |  |

Please email or FAX us of your detailed information for a prompt, satisfactory and constant service.

| <b>Detailed Company Information</b> |                                                      |                    |  |  |

|-------------------------------------|------------------------------------------------------|--------------------|--|--|

| Company/Organization                |                                                      |                    |  |  |

| Contact Person                      |                                                      |                    |  |  |

| E-mail Address                      |                                                      |                    |  |  |

| Address                             |                                                      |                    |  |  |

| Country                             |                                                      |                    |  |  |

| TEL                                 |                                                      | FAX                |  |  |

| Web Site                            |                                                      |                    |  |  |

|                                     | Ques                                                 | tions              |  |  |

| Product Model                       |                                                      |                    |  |  |

|                                     | OS:<br>Computer Brar<br>M/B:                         | CPU:               |  |  |

| Environment to Use                  | Chipset:<br>Video Card:<br>Network Interfa<br>Other: | BIOS:<br>ace Card: |  |  |

| Detail Description                  |                                                      |                    |  |  |

| Suggestions to ADLINK               |                                                      | _                  |  |  |

# **Table of Contents**

| Introd | luction                                           | 1  |

|--------|---------------------------------------------------|----|

| 1.1    | APPLICATIONS                                      | 2  |

| 1.2    | FEATURES                                          | 2  |

| 1.3    | SPECIFICATIONS                                    | 3  |

| 1.4    | SOFTWARE SUPPORTING                               | 5  |

|        | 1.4.1 Programming Library                         | 5  |

|        | 1.4.2 PCIS-LVIEW: LabVIEW® Driver                 | 5  |

|        | 1.4.3 PCIS-VEE: HP-VEE Driver                     | 6  |

|        | 1.4.4 DAQBench <sup>™</sup> : ActiveX Controls    | 6  |

| Instal | lation                                            | 7  |

| 2.1    | What You Have                                     | 7  |

| 2.2    | Unpacking                                         | 8  |

| 2.3    | DEVICE INSTALLATION FOR WINDOWS SYSTEMS           | 8  |

| 2.4    | PCI-7300A's LAYOUT                                | 9  |

| 2.5    | HARDWARE INSTALLATION OUTLINE                     | 10 |

| 2.6    | CONNECTOR PIN ASSIGNMENT                          |    |

| 2.7    | WIRING AND TERMINATION                            |    |

| 2.8    | DAUGHTER BOARD SUPPORTING                         |    |

|        | 2.8.1 Connect with DIN-100S                       |    |

|        | 2.8.2 Connect with DIN-502S                       |    |

| Regis  | ters                                              | 15 |

| 3.1    | I/O PORT BASE ADDRESS                             | 16 |

| 3.2    | DI_CSR: DI CONTROL & STATUS REGISTER              | 17 |

| 3.3    | DO_CSR: DO CONTROL & STATUS REGISTER              | 18 |

| 3.4    | AUXILIARY DIGITAL I/O REGISTER                    |    |

| 3.5    | INT_CSR: INTERRUPT CONTROL AND STATUS REGISTER    | 20 |

| 3.6    | DI_FIFO: DI FIFO DIRECT ACCESS PORT               |    |

| 3.7    | DO_FIFO: DO EXTERNAL DATA FIFO DIRECT ACCESS PORT |    |

| 3.8    | FIFO_CR: FIFO ALMOST EMPTY/FULL REGISTER          |    |

| 3.9    |                                                   |    |

|        | PLX PCI-9080 DMA CONTROL REGISTERS                |    |

| Opera  | tion Theory                                       | 25 |

| 4.1    | I/O CONFIGURATION                                 | 25 |

| 4.2    | BLOCK DIAGRAM                                     | 26 |

|   | 4.3                  | DIGITAL I/O DATA FLOW                                                                                                   | 27                   |

|---|----------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------|

|   | 4.4                  | INPUT FIFO AND OUTPUT FIFO                                                                                              | 28                   |

|   | 4.5                  | Bus-mastering DMA                                                                                                       | 29                   |

|   | 4.6                  | Scatter/gather DMA                                                                                                      | 30                   |

|   | 4.7                  | CLOCKING MODE                                                                                                           | 31                   |

|   | 4.8                  | STARTING MODE                                                                                                           | 32                   |

|   | 4.9                  | ACTIVE TERMINATOR                                                                                                       | 33                   |

|   | 4.10                 | DIGITAL INPUT OPERATION MODE                                                                                            | 33                   |

|   |                      | 4.10.1 Digital Input DMA in Internal Clock Mode                                                                         | 33                   |

|   |                      | 4.10.2 Digital Input DMA in External Clock Mode                                                                         | 35                   |

|   |                      | 4.10.3 Digital Input DMA in Handshaking Mode                                                                            | 37                   |

|   |                      | 4.10.4 Continuous Digital Input                                                                                         | 39                   |

|   | 4.11                 | DIGITAL OUTPUT OPERATION MODE                                                                                           | 40                   |

|   |                      | 4.11.1 Digital Output DMA in Internal Clock Mode                                                                        | 40                   |

|   |                      | 4.11.2 Digital Output DMA in Handshaking Mode                                                                           |                      |

|   |                      | 4.11.3 Digital Output DMA in Burst Handshaking Mode                                                                     | 43                   |

|   |                      | 4.11.4 Pattern Generator                                                                                                | 44                   |

|   | 4.12                 | Auxiliary DIO                                                                                                           | 45                   |

| C | C++                  | Libraries                                                                                                               | 46                   |

| • |                      |                                                                                                                         |                      |

|   | 5.1                  | LIBRARIES INSTALLATION                                                                                                  |                      |

|   | 5.2                  | PROGRAMMING GUIDE                                                                                                       |                      |

|   |                      | 5.2.1 Naming Convention                                                                                                 |                      |

|   |                      | 5.2.2 Data Types                                                                                                        |                      |

|   |                      | _7300_Initial                                                                                                           |                      |

|   |                      | _7300_CLOSE                                                                                                             |                      |

|   |                      | _7300_CONFIGURE                                                                                                         |                      |

|   |                      | _7300_DI_MODE                                                                                                           |                      |

|   |                      | _7300_DO_MODE                                                                                                           |                      |

|   | 5.8                  | _7300_AUX_DI                                                                                                            | 53                   |

|   | 5.9                  | _7300_AUX_DI_CHANNEL                                                                                                    | 53                   |

|   |                      | _7300_AUX_DO                                                                                                            |                      |

|   |                      | 7000 ALIV DO 0                                                                                                          | 54                   |

|   |                      | _7300_AUX_DO_CHANNEL                                                                                                    |                      |

|   |                      | _7300_ALLOC_DMA_MEM                                                                                                     | 55                   |

|   |                      |                                                                                                                         | 55<br>56             |

|   | 5.14                 | _7300_ALLOC_DMA_MEM                                                                                                     | 55<br>56<br>56       |

|   | 5.14<br>5.15         | _7300_ALLOC_DMA_MEM<br>_7300_FREE_DMA_MEM<br>_7300_DI_DMA_START<br>_7300_DI_DMA_STATUS                                  | 55<br>56<br>56<br>59 |

|   | 5.14<br>5.15<br>5.16 | _7300_ALLOC_DMA_MEM<br>_7300_FREE_DMA_MEM<br>_7300_DI_DMA_START<br>_7300_DI_DMA_STATUS<br>_7300_DI_DMA_ABORT            | 55<br>56<br>56<br>59 |

|   | 5.14<br>5.15<br>5.16 | _7300_ALLOC_DMA_MEM _7300_FREE_DMA_MEM _7300_DI_DMA_START _7300_DI_DMA_STATUS _7300_DI_DMA_ABORT _7300_GETOVERRUNSTATUS | 55<br>56<br>59<br>59 |

| 5.19 _7300_DO_DMA_STATUS                    | 62  |

|---------------------------------------------|-----|

| 5.20 _7300_DO_DMA_ABORT                     | 62  |

| 5.21 _7300_DO_PG_START                      | 63  |

| 5.22 _7300_DO_PG_STOP                       | 64  |

| 5.23 _7300_DI_TIMER                         |     |

| 5.24 _7300_DO_TIMER                         | 65  |

| 5.25 _7300_INT_TIMER                        | 65  |

| 5.26 _7300_GET_SAMPLE                       | 66  |

| 5.27 _7300_Set_Sample                       | 67  |

| 5.28 _7300_GetUnderrunStatus                | 67  |

| Appendix A 8254 Programmable Interval Times | r69 |

| A.1 The Intel (NEC) 8254                    | 69  |

| A.2 THE CONTROL BYTE                        | 69  |

| A.3 Mode Definition                         | 71  |

| Warranty Policy                             | 73  |

|                                             |     |

# **How to Use This Guide**

This manual is designed to help you use the cPCI-7300 and PCI-7300A Rev.B. The manual describes how to modify various settings on the PCI-7300A card to meet your requirements. It is divided into five chapters:

- **Chapter 1**, "Introduction", gives an overview of the product features, applications, and specifications.

- Chapter 2, "Installation", describes how to install the PCI-7300A. The layout of PCI-7300A is shown, and the installation procedures, pin assignment of connectors, and timer pacer generation are specified.

- Chapter 3, "Register Structure & Format", describes the low-level register structure and format of the PCI-7300A.

- Chapter 4, "Operation Theory", describes how to use the operations of digital input and output on the PCI-7300A.

- Chapter 5, "C/C++ & DLL Library", describes the high level C and DLL library functions. It will help you to programming in DOS, Win 3.11, Win-95 and Win-NT environments.

- Appendix A, "8254 Programmable Interval Timer", describes the detailed structure and register format of 8254-timer/counter chip.

# Introduction

The cPCI/PCI-7300A is cPCI/PCI form factor ultra-high speed digital I/O card, it consists of 32 digital input or output channel. High performance designs and the state-of-the-art technology make this card to be ideal for high speed digital input and output applications.

The cPCI/PCI-7300A performs high-speed data transfers using bus mastering DMA and scatter/gather via 32-bit PCI bus architecture. The maximum data transfer rates can be up to 80MB per second. It is very suitable for interface between high speed peripherals and your computer system.

The cPCI/PCI-7300A is configured as two ports, PORTA and PORTB, each port controls 16 digital I/O lines. The I/O can configure as either input or output, and 8-bit or 16-bit. According to outside device environment, users can configure cPCI/PCI-7300A to meet all high speed digital I/O data transfer.

There are 4 different digital I/O operation modes are supported:

- **1. Internal Clock:** the digital input and output operations are paced by internal clock and transferred by bus mastering DMA.

- **2. External Clock:** the digital input operation is paced by external strobe signal ( DIREQ ) and transferred by bus mastering DMA.

- **3. Handshaking:** through REQ signal and ACK signal, the digital I/O data can have simple handshaking data transfer.

- **4. Pattern Generation:** You can output a digital pattern repeatedly at a predetermined rate. The transfer rate is controlled by internal timer.

#### 1.1 Applications

- Interface to high-speed peripherals

- High-speed data transfers from other computers

- Automated test equipment (ATE)

- Electronic and logic testing

- Interface to external high-speed A/D and D/A converter

- Digital pattern generator

- Waveform and pulse generation

- Parallel digital communication

#### 1.2 Features

The PCI-7300A Ultra-High Speed DIO card provides the following advanced features:

- 32 digital input/output channels

- Extra 4-bit TTL digital input and output channels

- Transfer up to 80M Bytes per second

- SCSI active terminator for high speed and long distance data transfer

- 32-bit PCI bus

- Plug and Play

- Scatter/gatter DMA

- On-board internal clock generator

- Internal timer/external clock controls input sampling rate

- Internal timer control digital output rate

- ACK and REQ for handshaking

- TRIG signal controls start of data acquisition/pattern generation

- On-board 64KB FIFO

- 100-pin SCSI style connector

#### 1.3 Specifications

- ◆ Digital I/O (DIO)

- Numbers of Channel: 32 TTL compatible inputs and/or outputs

- Device: IDT 74FCT373

- I/O Configurations:

16 DI & 16 DO

32 DI

32 DO

#### ♦ Input Voltage:

- Low: Min. 0V: Max. 0.8V

- High: Min. +2.0V

#### Input Load:

Terminator OFF:

Low: +0.5V @ ±20 mA

High: +2.7V @ ±1 mA max.

Terminator ON:

Termination resistor: 110 Ohms

Termination voltage: 2.9V

Low: +0.5V @ ±22.4mA

High: +2.7V @ ± 1mA max.

#### Output Voltage:

- Low: Min. 0V; Max. 0.5V

- High: Min. +2.7V

#### Driving Capacity:

- Low: Max. +0.5V at 48mA (Sink)

- High: Min. 2.4V at -8 mA (Source)

- ♦ Hysteresis: 500mV

- Transfer Characteristic

- Mode: Bus Mastering DMA with Scatter/Gather

- Data Transfers: 8/16/32-bit input or output (programmable)

#### DMA Transfer count:

- 2M double words (8M bytes) for non-chaining mode DMA

- No limitation for chaining mode (scatter/gather) DMA

#### Max. Transfer rate:

- DO: 80M Bytes/sec: 32-bit output @ 20 MHz

- DI: 80M Bytes/sec: 32-bit input @ 20 MHz

#### • Programmable Counter:

- Device: 82C54-10

- Digital Input Pacer: 20MHz, 10MHz, or clock output of Timer #0

- Digital Output Pacer: 20MHz, 10MHz, or clock output of Timer #1

- General Purpose Timer: Output of Timer #2

- General Specifications

- ♦ Connector: one 100-pin male SCSI-II style cable connector

- **◆ Operating Temperature:** 0° C ~ 60°C

- ♦ Storage Temperature: -20° C ~ 80°C

- ♦ Humidity: 5 ~ 95%, non-condensing

- ◆ Dimension: Compact size only 179mm(L) X 102mm(H)

#### Power Consumption:

- +5 V @ 830 mA max. with on-board terminator off

- +5 V @ 1.0A max. with on-board terminator on

#### 1.4 Software Supporting

ADLINK provides versatile software drivers and packages for users' different approach to built-up a system. We not only provide programming library such as DLL for many Windows systems, but also provide drivers for software packages such as LabVIEW<sup>®</sup>, HP VEE<sup>TM</sup>, DASYLab<sup>TM</sup>, InTouch<sup>TM</sup>, InControl<sup>TM</sup>, ISaGRAF<sup>TM</sup>, and so on.

All the software options are included in the ADLINK CD. The non-free software drivers are protected with serial licensed code. Without the software serial number, you can still install them and run the demo version for two hours for demonstration purpose. Please contact with your dealer to purchase the formal license serial code.

#### 1.4.1 Programming Library

For customers who are writing their own programs, we provide function libraries for many different operating systems, including:

- ◆ DOS Library: Borland C/C++ and Microsoft C++, the functions descriptions are included in this user's guide.

- Windows 95 DLL: For VB, VC++, Delphi, BC5, the functions descriptions are included in this user's guide.

- PCIS-DASK: Include device drivers and DLL for Windows 98. Windows NT and Windows 2000. DLL is binary compatible across Windows 98. Windows NT and Windows 2000. That means all applications developed with PCIS-DASK are compatible across Windows 98. Windows NT and Windows 2000. The developing environment can be VB, VC++, Delphi, BC5, or any Windows programming language that allows calls to a DLL. The user's guide and function reference manual of PCIS-DASK are in the PDF CD Please refer the manual files under \\Manual PDF\Software\PCIS-DASK

The above software drivers are shipped with the board. Please refer to the "Software Installation Guide" to install these drivers.

#### 1.4.2 PCIS-LVIEW: LabVIEW<sup>®</sup> Driver

PCIS-LVIEW contains the VIs, which are used to interface with NI's LabVIEW software package. The PCIS-LVIEW supports Windows 95/98/NT/2000. The LabVIEW drivers are free shipped with the board. You can install and use them without license. For detail information about PCIS-LVIEW, please refer to the user's guide in the CD.

(\\Manual\_PDF\Software\PCIS-LVIEW)

#### 1.4.3 PCIS-VEE: HP-VEE Driver

The PCIS-VEE includes the user objects, which are used to interface with HP VEE software package. PCIS-VEE supports Windows 95/98/NT. The HP-VEE drivers are free shipped with the board. You can install and use them without license. For detail information about PCIS-VEE, please refer to the user's quide in the CD.

(\Manual PDF\Software\PCIS-VEE)

#### 1.4.4 DAQBench™: ActiveX Controls

We suggest the customers who are familiar with ActiveX controls and VB/VC++ programming use the DAQBench<sup>TM</sup> ActiveX Control components library for developing applications. The DAQBench<sup>TM</sup> is designed under Windows NT/98. For more detailed information about DAQBench, please refer to the user's guide in the CD.

(\Manual PDF\Software\DAQBench\DAQBench Manual.PDF)

# Installation

This chapter describes how to install the cPCI/PCI-7300A. At first, the contents in the package and unpacking information that you should be careful are described. Because the PCI-7300A is following the PCI design philosophy, it is no more jumpers and DIP switches setting for configuration. The Interrupt and I/O port address are the variables associated with automatic configuration, the resource allocation is managed by the system BIOS. Upon system power-on, the internal configuration registers on the board interact with the BIOS.

#### 2.1 What You Have

In addition to this *User's Manual*, the package includes the following items:

- cPCI/PCI-7300A 80MB Ultra-High Speed 32-CH Digital I/O Card

- ADLINK All-in-one CD

- Software Installation Guide

If any of these items is missing or damaged, contact the dealer from whom you purchased the product. Save the shipping materials and carton in case you want to ship or store the product in the future.

#### 2.2 Unpacking

Your cPCI/PCI-7300A card contains sensitive electronic components that can be easily damaged by static electricity.

The card should be placed on a grounded anti-static mat. The operator should be wearing an anti-static wristband, grounded at the same point as the anti-static mat.

Inspect the card module carton for obvious damage. Shipping and handling may cause damage to your module. Be sure there are no shipping and handling damages on the module before processing.

After opening the card module carton, extract the system module and place it only on a grounded anti-static surface component side up.

Again inspect the module for damage. Press down on all the socketed IC's to make sure that they are properly seated. Do this only with the module place on a firm flat surface.

Note: DO NOT APPLY POWER TO THE CARD IF IT HAS BEEN DAMAGED.

You are now ready to install your cPCI/PCI-7300A.

# 2.3 Device Installation for Windows Systems

Once Windows 95/98/2000 has started, the Plug and Play function of Windows system will find the new NuDAQ/NuIPC cards. If this is the first time to install NuDAQ/NuIPC cards in your Windows system, you will be informed to input the device information source. Please refer to the "Software Installation Guide" for the steps of installing the device.

# 2.4 PCI-7300A's Layout

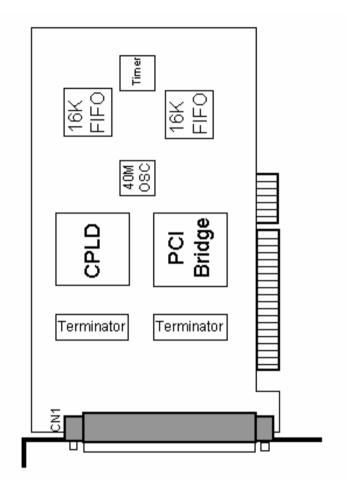

Figure 2.1 PCI-7300A Layout Diagram

Figure 2.2 cPCI-7300A Layout Diagram

#### 2.5 Hardware Installation Outline

#### PCI configuration

The PCI cards (or *CompactPCI* cards) are equipped with plug and play PCI controller, it can request base addresses and interrupt according to PCI standard. The system BIOS will install the system resource based on the PCI cards' configuration registers and system parameters (which are set by system BIOS). Interrupt assignment and memory usage (I/O port locations) of the PCI cards can be assigned by system BIOS only. These system resource assignments are done on a board-by-board basis. It is not suggested to assign the system resource by any other methods.

#### PCI slot selection

Please note that the PCI slot must provide bus-mastering capability to operate this board well.

#### Installation Procedures

- 1. Turn off your computer.

- 2. Turn off all accessories (printer, modem, monitor, etc.) connected to your computer.

- 3. Remove the cover from your computer.

- 4. Select a 32-bit PCI slot. PCI slots are short than ISA or EISA slots, and are usually white or ivory.

- Before handling the PCI cards, discharge any static buildup on your body by touching the metal case of the computer. Hold the edge and do not touch the components.

- 6. Position the board into the PCI slot you selected.

- 7. Secure the card in place at the rear panel of the system.

# 2.6 Connector Pin Assignment

The PCI-7300A comes equipped with one 100-pin SCSI type connector (CN1) located on the rear mounting plate. The pin assignment of CN1 is illustrated in the figure 2.2.

Legend:

| Legena: |             |             |                     |                                                                                                                                                                    |

|---------|-------------|-------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pins    | Signal Name | Signal Type | Signal<br>Direction | Description                                                                                                                                                        |

| 150     | GND         | GND         |                     | Ground – these lines are the ground reference for all other signals                                                                                                |

| 5166    | PB15PB0     | DATA        | I/O                 | PortB bidirectional data liness-PB15 is the MSB, and PB0 is the LSB.                                                                                               |

| 67      | DOACK       | CONTROL     | I                   | Digital output Acknowledge lines – In handshaking mode, DOACK carries handshaking status information from the peripheral.                                          |

| 68      | DOREQ       | CONTROL     | 0                   | Request line – In handshaking mode, DOREQ carries handshaking control information to peripheral.                                                                   |

| 69      | DOTRIG      | CONTROL     | -                   | DO TRIG- can be used to control the start of data output in all DO modes and to control the stop of pattern generation in pattern generation mode.                 |

| 7073    | AUXDO30     | DATA        | 0                   | AUX DO 30 – can be used as extra output data or can be used as extra control signals.                                                                              |

| 85100   | PA15PA0     | DATA        | I/O                 | PortA bidirectional data liness-PA15 is the MSB, and PA0 is the LSB.                                                                                               |

| 82      | DIACK       | CONTROL     | 0                   | Digital output Acknowledge lines – In handshaking mode, DIACK carries handshaking status information to the peripheral.                                            |

| 83      | DIREQ       | CONTROL     | I                   | Request line – In handshaking mode, DIREQ carries handshaking control information from peripheral. In external clock mode, DIREQ carries the external clock input. |

| 84      | DITRIG      | CONTROL     | I                   | DI TRIG – can be used to control the start of data acquisition in all DI modes.                                                                                    |

| 7881    | AUXDI30     | DATA        | I                   | AUX DI 30 – can be used as extra input data or can be used as extra control signals.                                                                               |

| 7477    | TERMPWR     | POWER       |                     | TERMPWR 4.7V active terminator power output                                                                                                                        |

#### 2.7 Wiring and Termination

Transmission line effects and environment noise, particularly on clock and control lines, can lead to incorrect data transfers if you do not take care when running signal wires to and from the devices.

Take the following precautions to ensure a uniform transformation line and minimize noise pickup:

- Use twisted-pair wires to connect digital I/O signals to the device. Twist each digital I/O signal with a GND line. In PCI-7300A, 50 signals are used as GND.

- 2. Place a shield around the wires connecting digital I/O signal to device.

- 3. Route signals to the devices carefully. Keep cabling away from noise sources, such as video monitor.

For cPCI/PCI-7300A, it is important to terminate your cable properly to reduce or eliminate signal reflections in the cable. The PCI-7300A support active terminator on board, you can enable or disable the terminator by software selection. This is a good way to include termination on the signal transmission.

Additional recommendations apply for all signal connection to your cPCI/PCI-7300A are listed as follows:

- 1. Separate cPCI/PCI-7300A device signal lines from high-current or high-voltage line. These lines are capable of inducing currents in or voltages on the cPCI/PCI-7300A if they run in parallel paths at a close distance. To reduce the magnetic coupling between lines, separate them by a reasonable distance if they run in parallel, or run the lines at right angles to each other.

- 2. Do not run signal lines through conducts that also contain power lines.

- 3. Protect signal lines from magnetic fields.

#### 2.8 Daughter Board Supporting

The cPCI/PCI-7300A can be connected with two daughter boards: DIN-100S or DIN-502S. The functionality and connections are specified as follows.

#### 2.8.1 Connect with DIN-100S

The DIN-100S is a direct connection for the add-on card that is equipped with SCSI-100 connector. User can connect this daughter board by a 100-pin SCSI type cable (ACL-102100) to the cPCI/PCI-7300A. It is suitable for the applications of 32-bit digital input or 32-bit digital output.

#### 2.8.2 Connect with DIN-502S

The DIN-502S with the cable ACL-10252 separates the 100-pin SCSI connector into two 50-pin SCSI connectors. One 50 pin connector is for pin 1  $\sim$  25 and pin 51 $\sim$ 75 of CN1 while the other one is for pin 26  $\sim$  50 and pin 76 $\sim$ 100 of CN1. That means the DIN-502S and the ACL-10252 make users easy to connect the 16-bit digital inputs and 16-bit digital outputs by using two 50-pin daughter boards respectively. The independent wiring of 16-bit DI and 16-bit DO let users convenient to setup and maintain his systems.

# **Registers**

In this chapter, the registers' format of the cPCI/PCI-7300A is described. Please note that the registers' map of the PCI-7300A Rev.B is different from the PCI-7300A Rev.A

This information is quite useful for the programmers who wish to handle the card by low-level programming. In addition, users can realize how to use software driver to manipulate this card after understanding the registers' structure of the cPCI/PCI-7300A

The cPCI/PCI-7300A functions as a 32-bit PCI master device on the PCI bus. There are three types of registers on the cPCI/PCI-7300A: PCI Configuration Registers (PCR), Local Configuration Registers (LCR) and cPCI/PCI-7300A's registers.

The PCR, which compliant to the PCI-bus specifications, is initialized and controlled by the plug & play (PnP) PCI BIOS. User's can study the PCI BIOS specification to understand the operation of the PCR. Please contact with PCISIG to acquire the specifications of the PCI interface.

The LCR is specified by the PCI bus controller PLX PCI-9080, which is provided by PLX technology Inc. (www.plxtech.com) . It is not necessary for users to understand the details of the LCR if you use the software library. The base address of the LCR is assigned by the PCI PnP BIOS. The assigned address is located at offset 14h of PCR.

#### 3.1 I/O Port Base Address

The registers of the cPCI/PCI-7300A are shown in Table 3.1. The base address of these registers is also assigned by the PCI P&P BIOS. The assigned base address is stored at offset 18h of the PCR. Therefore, users can read the PCR to know the base address by using BIOS function call. Note that the cPCI/PCI-7300A registers are all 32 bits. Users should access these registers by 32 bits I/O instructions.

The PCI-7300A occupies 8 consecutive 32-bit I/O addresses in the I/O address space. Table 3.1 shows the I/O Map of the PCI-7300A rev.B.

| Address   | Read         | Write        |

|-----------|--------------|--------------|

| Base + 0  | DI_CSR       | DI_CSR       |

| Base + 4  | DO_CSR       | DO_CSR       |

| Base + 8  | AUX_DIO      | AUX_DIO      |

| Base + C  | INT_CSR      | INT_CSR      |

| Base + 10 | DI_FIFO      | DI_FIFO      |

| Base + 14 | DO_FIFO      | DO_FIFO      |

| Base + 18 | -            | FIFO_CR      |

| Base + 1C | POL_CTRL     | POL_CTRL     |

| Base + 20 | 8254_COUNT0  | 8254_COUNT0  |

| Base + 24 | 8254_COUNT1  | 8254_COUNT1  |

| Base + 28 | 8254_COUNT2  | 8254_COUNT2  |

| Base + 2C | 8254_CONTROL | 8254_CONTROL |

#### Legend:

DI\_CSR: Digital input control & status register DO\_SCR: Digital output control & status register

AUX DIO: Auxiliary digital I/O port

INT\_CSR: Interrupt control and status register

DI\_FIFO: DI FIFO direct access port DO\_FIFO: DO FIFO direct access port

FIFO\_CR: FIFO almost empty/full programming register POL\_CTRL: Polarity control register for the control signals

#### Caution:

1. I/O port is 32-bit width

2. 8-bit or 16-bit I/O access is not allowed.

#### 3.2 DI\_CSR: DI Control & Status Register

Digital input control and status checking is done by this register.

Address: BASE + 00 Attribute: READ/WRITE

#### Data Format:

| Bit # 3~0   | DI_HND_SHK   | DI_CLK_SEL      |                  | DI_32         |

|-------------|--------------|-----------------|------------------|---------------|

| Bit # 7~4   | 0            | PA_TERM_OF<br>F | DI_WAIT_TRI<br>G | (1)           |

| Bit # 11~8  | DI_FIFO_FULL | DI_OVER         | DI_FIFO_CLR      | DI_EN         |

| Bit # 15~12 | -            | -               | -                | DI-FIFO_EMPTY |

| Bit # 31~16 | Don't Cared  | •               |                  | •             |

(1) This bit is different between Rev.A and Rev.B.

#### DI 32 (R/W)

0: Input port is not 32-bit wide (16-bit or 8-bit wide)

1: Input port is 32-bit wide, PORTB is configured as the extension of PORTA. That means PORTA is input lines 0...15, and PORTB is input lines 16...31. All the PORTB control signals are disabled.

#### DI CLK SEL (R/W)

00: use timer0 output as input clock

01: use 20MHz clock as input clock

10: use 10MHz clock as input clock

11: use external clock (DI\_REQ) as input clock

## DI HND SHK (R/W)

0: No handshaking

1: REQ/ACK handshaking mode

#### DI\_WAIT\_TRIG (R/W)

0: start input sampling immediately

1: delay input sampling until DITRIG is active

#### PA\_TERM\_OFF (R/W)

0: PORTA terminator ON

1: PORTA terminator OFF

#### DI\_EN (R/W)

0: Disable digital inputs

1: Enable digital inputs

#### DI FIFO CLR (R/W)

0: No effect

1: Clear digital input FIFO. If both PORTA and PORTB are configured as inputs, both FIFO will be cleared. Always get 0 when read.

#### DI OVER (R/W)

0: DI FIFO does not full during input sampling

1: DI FIFO full during input sampling, some input data was lost, write "1" to clear this bit

#### DI FIFO FULL (RO)

0: DI FIFO is not full

1: DI FIFO is full

#### DI\_FIFO\_EMPTY (RO)

0: DI FIFO is not empty

1: DI FIFO is empty

#### 3.3 DO\_CSR: DO Control & Status Register

Digital input control and status checking is done by this register.

Address: BASE + 04

Attribute: READ/WRITE

#### **Data Format:**

| Bit # 3~0   | DO_WAIT_NAE  | DO_MODE     |                 | DO_32         |

|-------------|--------------|-------------|-----------------|---------------|

| Bit # 7~4   | PG_STOP_TRIG | PB_TERM_OFF | DO_WAIT_TRG     | PAT_GEN       |

| Bit # 11~8  | DO_FIFO_FULL | DO_UNDER    | DO_FIFO_CLR     | DO_EN         |

| Bit # 15~12 | -            | -           | BURST_HNDSH (2) | DO_FIFO_EMPTY |

| Bit # 31~16 | Don't Cared  |             |                 |               |

(2) This bit is different between Rev.A and Rev.B.

#### DO 32 (R/W)

0: Output port is not 32-bit wide (16-bit or 8-bit wide)

1: Output port is 32-bit wide, PORTA is configured as the extension of PORTB. That means PORTB is output lines (0...15), and PORTA is output lines (16...31). All PORTA control signals are disabled.

#### DO\_MODE (R/W)

00: use timer1 output as output clock

01: use 20MHz clock as output clock

10: use 10MHz clock as output clock

11: REQ/ACK handshaking mode

#### DO\_WAIT\_NAE (R/W)

- 0: do not wait output FIFO not almost empty flag

- 1: delay output data until FIFO is not almost empty

#### PAT GEN(R/W)

- 0: pattern generation disable (FIFO data do not repeat during data output)

- 1: pattern generation enable (FIFO data repeat themselves during data output)

#### DO WAIT TRIG (R/W)

- 0: start output data immediately

- 1: delay output data until DOTRIG is actived

#### PB TERM OFF (R/W)

- 0: PORTB terminator ON

- 1: PORTB terminator OFF

#### PG STOP TRIG (R/W)

- 0: no effect

- 1: Stop pattern generation when DOTRIG is deasserted

#### DO EN (R/W)

- 0: Disable digital outputs

- 1: Enabled digital outputs

#### DO\_FIFO\_CLR (R/W)

- 0: No effect

- 1: Clear digital output FIFO. If both PORTA and PORTB are configured as outputs, both FIFO will be cleared. Always get 0 when read.

#### DI UNDER (R/W)

- 0: DO FIFO does not empty during data output

- 1: DO FIFO is empty during data output, some output data may be output twice. Write 1 to clear this bit

#### DO FIFO FULL (RO)

- 0: DO FIFO is not full

- 1: DI FIFO is full

#### DO FIFO EMPTY (RO)

- 0: DO FIFO is not empty

- 1: DO FIFO is empty

#### BURST HNDSHK (R/W)

0: disable burst handshaking mode

1: enable burst handshake mode

#### 3.4 Auxiliary Digital I/O Register

Auxiliary 4-bit digital inputs and 4-bit digital outputs

Address: BASE + 08

Attribute: READ/WRITE

#### **Data Format:**

| Bit # 3~0  | DO_AUX_3    | DO_AUX_2 | DO_AUX_1 | DO_AUX_0 |

|------------|-------------|----------|----------|----------|

| Bit # 7~4  | DI_AUX_3    | DI_AUX_2 | DI_AUX_1 | DI_AUX_0 |

| Bit # 31~8 | Don't Cared |          |          |          |

This auxiliary digital I/O is controlled by porgram I/O only.

#### $DO_AUX_3 \sim DO_AUX_0 (R/W)$

4-bit auxiliary output port. Program I/O only.

#### $DI_AUX_3 \sim DI_AUX_0 (R)$

4-bit auxiliary input port. Program I/O only

# 3.5 INT\_CSR: Interrupt Control and Status Register

The interrupt of PCI-7300A is controlled and status is checked through this register.

Address: BASE + 0x0C Attribute: READ/WRITE

#### **Data Format:**

| Bit # 3~0  | T2_INT      | AUXIO_INT | T2_EN    | AUXDI0_EN |

|------------|-------------|-----------|----------|-----------|

| Bit # 7~4  | -           | -         | Reserved | Reserved  |

| Bit # 31~8 | Don't Cared | •         | •        |           |

#### AUXDI\_EN (R/W)

0: Disable AUXDI0 interrupt

1: Interrupt CPU on falling edge of AUXDI0

<sup>\*</sup> Note: This bit is for Rev.B only.

#### T2\_EN (R/W)

0: Disable Timer2 interrupt

1: Interrupt CPU on falling edge of Timer 2 output

#### AUXDIO INT (R/W)

0: AUXDI does not generate interrupt

1: AUXDI interrupt occurred. Write "1" to clear

#### T2 INT (R/W)

0: Timer 2 does not generate interrupt

1: Timer 2 interrupt occurred. Write "1" to clear

#### 3.6 DI FIFO: DI FIFO direct access port

The digital input FIFO data can be accessed through this port directly.

Address: BASE + 0x10

Attribute: READ/WRITE

#### **Data Format:**

| Bits        | 7          | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|------------|------|---|---|---|---|---|---|

| Bit # 7~0   | DI_FIF     | O_8  |   |   |   |   |   |   |

| Bit # 15~8  | DI_FIFO_16 |      |   |   |   |   |   |   |

| Bit # 31_16 | DI_FIF     | O_32 |   |   | • | • | • |   |

#### DI FIFO 8

Bit 7 ~ Bit 0 of digital input FIFO

#### DI\_FIFO\_16

Bit 15 ~ Bit 8 of digital input FIFO if the digital input is configured as 16-bit wide or 32-bit wide.

#### DI FIFO 32

Bit 31 ~ Bit 16 of digital input FIFO if the digital input is configured as 32-bit wide

Note: Although this port is R/W port, write operation should be avoided in normal operation. If both PORT A and PORT B are configured as output ports, read/write to this port is meaningless.

# 3.7 DO\_FIFO: DO external data FIFO direct access port

The digital output FIFO data can be accessed through this port directly.

Address: BASE + 0x0C Attribute: READ/WRITE

#### **Data Format:**

| Bits        | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|------------|---|---|---|---|---|---|---|

| Bit # 7~0   | DO_FIFO_8  |   |   |   |   |   |   |   |

| Bit # 15~8  | DO_FIFO_16 |   |   |   |   |   |   |   |

| Bit # 31_16 | DO_FIFO_32 |   |   |   |   |   |   |   |

#### DO FIFO 8

Bit 7 ~ Bit 0 of digital output FIFO

#### DO FIFO 16

Bit 15 ~ Bit 8 of digital output FIFO if the digital output is configured as 16-bit wide or 32-bit wide.

#### DO FIFO 32

Bit 31 ~ Bit 16 of digital output FIFO of the digital output is configured as 32-bit wide

Note: Although this port is R/W port, read operation should be avoided in normal operation. If both PORTA and PORTB are configured as input ports, read/write to this port is meaningless.

#### 3.8 FIFO\_CR: FIFO almost empty/full register

The register is used to control the FIFO programmable almost empty/full flag.

Address: BASE + 0x018 Attribute: WRITE Only

#### Data Format:

| Bits      | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|------------|---|---|---|---|---|---|---|

| Bit 15~0  | PB_PAE_PAF |   |   |   |   |   |   |   |

| Bit 31_16 | PA_PAE_PAF |   |   |   |   |   |   |   |

#### PB PAE PAF (WO)

Programmable almost empty/full threshold of PORTB FIFO, 2 consecutive writes are required to program PORTB FIFO. Programmable almost empty threshold first.

#### PA\_PAE\_PAF(WO)

Programmable almost empty/full threshold of PORTA FIFO, 2 consecutive writes are required to program PORTA FIFO. Programmable almost empty threshold first.

# 3.9 POL\_CNTRL: Control Signal Polarity Control Register

The register is used to control the control signals' polarity. The control signals include DI\_REQ, DI\_ACK, DI\_TRG, DO\_REQ, DO\_ACK and DO\_TRG. Please note that this register is for PCI-7300A Rev.B and cPCI-7300 only.

Address: BASE + 0x1C Attribute: READ/WRITE

#### **Data Format:**

| Bit # 3~0  | DO_REG_NEG  | DI_TRG_NEG | DI_ACK_NEG | DI_REQ_NEG |

|------------|-------------|------------|------------|------------|

| Bit # 71~4 | -           | -          | DO_TRG_NEG | DO_ACK_NEG |

| Bit # 31~8 | Don't Cared |            |            |            |

#### DI\_REQ\_NEQ (R/W)

0: DI\_REQ is rising edge active1: DI\_REQ is falling edge active

#### DI ACK NEQ (R/W)

0: DI ACK is rising edge active

1: DI\_ACK is falling edge active

#### DI\_TRG\_NEQ (R/W)

0: DI\_TRG is rising edge active

1: DI\_TRG is falling edge active

#### DO\_REQ\_NEQ (R/W)

0: DO\_REQ is rising edge active

1: DO\_REQ is falling edge active

#### DO\_ACK\_NEQ (R/W)

0: DO\_ACK is rising edge active

1: DO\_ACK is falling edge active

#### DO\_TRG\_NEQ (R/W)

0: DO\_TRG is rising edge active

1: DO\_TRG is falling edge active

# 3.10 PLX PCI-9080 DMA Control Registers

The registers of bus-mastering DMA as well as the control and status registers of PCI-bus interrupts are built in the PLX PCI-9080 ASIC. Users can refer to the manual of PLX PCI-9080 for detailed information.

# **Operation Theory**

This chapter provides the detailed operation information for the cPCI/PCI-7300A, including I/O configuration, block diagram, input/output FIFO, bus-mastering DMA, scatter/gather, clocking mode, starting mode, termination, I/O transfer mode, and auxiliary digital I/O.

## 4.1 I/O Configuration

The 32-bit I/O data path of PCI-7300A can be configured as 8-bit, 16-bit, or 32-bit, the possible configuration modes are listed as follows.

| Mode           | Channel          | Description              |

|----------------|------------------|--------------------------|

| DI32           | PORTA (DI0DI15)  | Both PORTA and PORTB     |

|                | PORTB (DI16DI31) | are configured as input  |

|                |                  | channel                  |

| DO32           | PORTA            | Both PORTA and PORTB     |

|                | (DO16DO31)       | are configured as output |

|                | PORTB            | channel                  |

|                | (DO0DO15)        |                          |

| DI16DO16       | PORTA (DI0DI15)  | PORTA is 16-CH input     |

| (default mode) | PORTB            | PORTB is 16-CH output    |

|                | (DO0DO15)        |                          |

| DI16DO8        | PORTA (DI0DI15)  | PORTA is 16-CH input     |

|                | PORTB (DO0DO7)   | PORTB is 8-CH output     |

| DI8DO16        | PORTA (DI0DI7)   | PORTA is 8-CH input      |

|                | PORTB            | PORTB is 16-CH output    |

|                | (DO0DO15)        |                          |

| DI8DO8         | PORTA (DI0DI7)   | PORTA is 8-CH input      |

|                | PORTB (DO0DO7)   | PORTB is 8-CH output     |

#### Notes:

PORTA is default as Input channel; PORTB is default as output channel.

In DI32 mode, the PORTB has to be configured as the extension of PORTA, that is, PORTB is the input port (DI16...DI31). PORTB control signals are disabled.

In DO32 mode, the PORTA has to be configured as the extension of PORTB, that is, PORTA is the output port (DO16...DO31). PORTA control signals are disabled.

DIO: input LSB, DI31: input MSB; DO0:output LSB, DO31:output MSB.

LSB: Least Significant Bit, MSB: Most Significant Bit

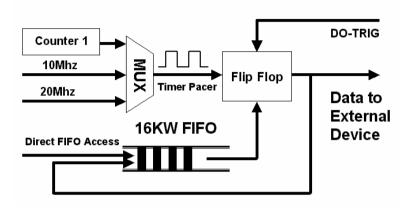

## 4.2 Block Diagram

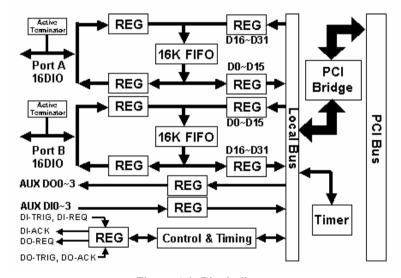

Figure 4.1 shows the block diagram of the cPCI/PCI-7300A, it includes the I/O registers, two 16K FIFOs, auxiliary DIO, active terminators, and so on.

Figure 4.1: Block diagram

PORTA: 16 Digital I/O Port, it can be set as terminated mode or

non-terminated mode

PORTB: 16 Digital I/O Port, it can be set as terminated mode or

non-terminated mode

FIFO: Two 16K words FIFO for digital I/O data buffer

AUX DO 3..0: Four auxiliary digital outputs

AUX DI 3..0: Four auxiliary digital inputs DITRIG: Digital input trigger line

DIACK/DIREQ: Digital input handshaking signals

DOTRIG: Digital output trigger line

DOACK/DOREQ: Digital output handshaking signals

#### 4.3 Digital I/O Data Flow

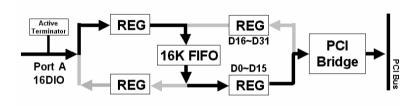

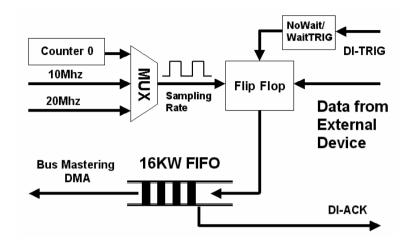

When applying digital input functions, the data will be sampled into the input FIFO periodically as we configured and then transfer to the system memory by the bus mastering DMA of the PCI Bridge. Figure 4.2 show the data flow of the 16-bit digital input operation.

Figure 4.2 Data flow of digital input

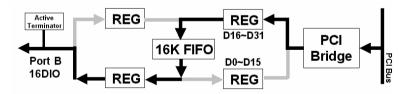

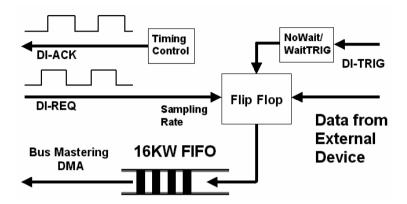

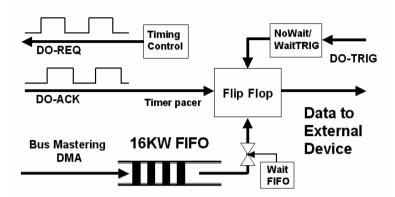

On the other hand, Figure 4.3 shows the data flow of 16-bit digital output operation. After the bus mastering DMA of the PCI Bridge transfers the output data to the output FIFO, the cPCI/PCI-7300A will output the data to the external devices in a pre-assigned period.

Figure 4.3 Data flow of digital output

The width of local data bus on the cPCI/PCI-7300A can be programmable to be 8-bit, 16-bit or 32-bit. The default data width is 16-bit. Port A is default to be input port, and Port B is default to be output one. When 8-bit data width is applied, only the lower byte of the bus will be used. While we program the data width to be 32-bit, the two ports will operate in the same manner.

#### 4.4 Input FIFO and Output FIFO

Due to the data transfer rate between external devices and the cPCI/PCI-7300A is independent from that between cPCI/PCI-7300A and PCI bus. Two 16K words FIFO are provided to be I/O buffers.

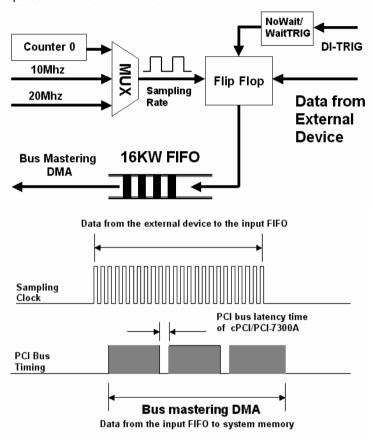

For digital input operation, data is sampled and transferred to the input FIFO. When the input FIFO is non-empty, the PCI bridge will automatically transfer the data from the input FIFO to the system memory in the background when PCI bus is available.

As the data transfer rate from external device to input FIFO (DI pre-transfer rate) is lower than that from input FIFO to system memory (DI post-transfer rate), the input FIFO is usually empty. On the contrary, when DI pre-transfer rate is higher than DI post-transfer rate, the FIFO becomes full and the overrun situation occurs if the data size is larger than the FIFO size, that is 16K samples. When DI overrun happens, the next input data will lose until the input FIFO becomes non-full once again. Users can check the overrun status by using the function  $\_7300\_GetOverrunStatus$ .

For digital output operation, data is moved from system memory to the output FIFO by bus mastering DMA, assume the data transfer rate is DO pre-transfer rate. Then, the data will be transferred to the external devices periodically as we configured, assume the transfer rate is DO post-transfer rate. When the DO pre-transfer rate is higher than the DO post-transfer rate, the DMA transfer stops as the output FIFO becomes full. On the contrary, if DO pre-transfer rate is lower than DO post-transfer rate. The underrun situation occurs as the output FIFO becomes empty. The output data remains when underrun happens. User can check the underrun status by using the function 7300 GetUnderrunStatus.

Notes: The max data length should be 16K instead of 32K. Users can send repetitive pattern of 8-/16-/32-bit width with a length of 16K samples, because of the FIFO depth is as it is no matter how wide the bus. Users should remember that the FIFO chip size is 32K bytes with 16-bits width. Therefore, for each bit, the depth is 16K.

If you need more depth of data, the data have to be in the PC memory and chain the pattern memory circularly, and then do chaining mode DMA which will generate the desired pattern repetitively.

# 4.5 Bus-mastering DMA

Digital I/O data transfer between PCI-7300A and PC's system memory is through bus mastering DMA, which is controlled by PCI bridge chip PLX PCI-9080. The PCI bus master means the device requires fast access to the bus or high data throughput in order to achieve good performance.

However, users should note that when more than one bus masters request the bus ownership, all masters will share the bandwidth of PCI bus and the performance of each master will unavoidably drop. Therefore, in order to obtain the maximum data throughput of the cPCI/PCI-7300A, it is recommended to remove or disable the bus mastering function of other bus masters, such as network, SCSI, modem adapters, and so on.

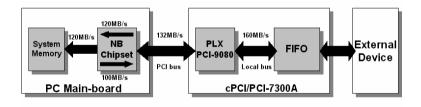

The maximum data throughput of the cPCI/PCI-7300A is also limited by the data throughput of the bridge chipset (North Bridge: NB) between PCI bus and system memory. The typical data throughput of NB chipset is 120MB/s for input and 100MB/s for output. Please refer to the figure 4.6. User should check the specs of the chipset on your main-board to determine the cPCI/PCI-7300A's maximum data throughput. The 80MB/s data throughput of the cPCI/PCI-7300A is guaranteed in the pervious system setup by using the internal 20MHz-sampling rate.

Figure 4.6: Maximum data throughput

From figure 4.6, we can find that NB chipset is the bottleneck of the maximum data transfer rate as only one bus master exists. When the transfer rate users required is smaller than the maximum transfer rate, by using scatter/gather (see 4.6), users can transfer the maximum data size as they have on their system memory. However, if the data should be real-time saved to the hard-disk rather than memory, the bottleneck would be the data transfer rate of the hard-disk driver.

# 4.6 Scatter/gather DMA

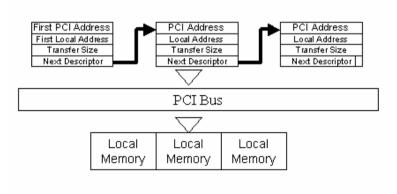

The PCI Bridge also supports the function of scatter/gather bus mastering DMA, which helps the users to transfer a large amount of data by linking the all memory blocks into a continuous linked list.

In the multi-user or multi-tasking OS, like Microsoft Windows, Linux, and so on. It is difficult to allocate a large continuous memory block to do the DMA transfer. Therefore, the PLX PCI-9080 provides the function of scatter/gather or chaining mode DMA to link the non-continuous memory blocks into a linked list so that users can transfer a very large amount of data without limiting by the fragment of small size memory. Users can configure the linked list for the input DMA channel or the output DMA channel. The figure 4.7 shows the linked list that is constructed by three DMA descriptors. Each descriptor contains a PCI address, a local address, a transfer size, and the pointer to the next descriptor. Users can allocate many small size memory blocks and chain their associative DMA descriptors altogether bν their application programs. cPCI/PCI-7300A's software driver provides the easy settings of the scatter/gather function, and some sample programs are also provided within the ADLink all-in-one CD. Users can refer to these sample programs and the function 5.14 and 5.18 for more detailed description.

Figure 4.7: Scatter/gather DMA for digital output

In non-chaining mode, the maximum DMA data transfer size is 2M double words (8M bytes). However, by using chaining mode, scatter/gather, there is no limitation on DMA data transfer size. Users can also link the descriptor nodes circularly to achieve a double-buffered mode DMA.

# 4.7 Clocking Mode

The data input to or output from the FIFO is operated in a specific rate. The specific sampling rate or the pacer rate can be programmable by software, by external clock, or by easy handshaking protocol.

Four clocking modes are provided in the cPCI/PCI-7300A to sample input data to the FIFO or output date from FIFO to the external devices. They are:

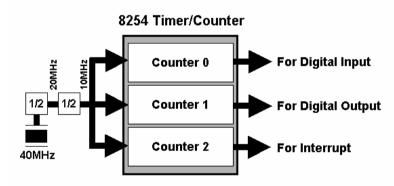

1. Internal Clock: Three sources are available to activate both digital input and digital output. They are 20MHz, 10MHz, and programmable timer 82C54. There are three counters in 82C54, counter 0 is used to generate sampling clock for digital input, counter 1 is used timer pacer for digital output, and counter 2 is used for interrupt function. The configuration is illustrated as follows.

Figure 4.8: Timer configuration

2. External Clock: This mode is only applied for digital input. The digital inputs are handled by the external clock strobe (DI-REQ). The DI-ACK signal reflects the almost full status of the input FIFO. The DI-ACK is asserted when input FIFO is not almost full, which means the external device can input data. If the input FIFO is almost full, the DI-ACK is de-asserted, then the external device should pause data transfer and wait

for the assertion of DI-ACK. If the external device follows the rule, there would be no data lost due to FIFO overrun.

- 3. Handshaking: For the digital input, through DI-REQ input signal from external device and DI-ACK output signal to the external device, the digital input can have simple handshaking data transfer. For the digital output, through DO-REQ output signal to the dexternal device and DO-ACK input signal from external device, the digital output can have simple handshaking data transfer

- 4. Burst Handshaking: This mode is available for both digital output and digital input. If the digital output DMA use internal clock and the burst handshaking mode is enable, the cPCI/PCI-7300A output data only when DO-ACK is asserted. That is, the external device can control the data input from the cPCI/PCI-7300A by asserting the DO-ACK pin when it is ready to receive data.

The software driver functions of 5.6 and 5.7 are provided to setup the clocking mode of digital input and digital output, respectively.

Notes: Due to the internal clock is based on 10MHz clock, some specific sampling rate or pacer rate cannot be generated by software, such as 9MHz. For digital input, users can use the external clock source. However, for digital output, users should replace the default 40MHz oscillator because the current version of cPCI/PCI-7300A does not support external clock for digital output.

The frequency of external input clock cannot exceed 40MHz due to the local bus timing requirement.

When users replace the default oscillator on board, the corresponding frequency would be changed, for example, by replacement with 36Mhz oscillator, the internal clock selection would be changed to 18MHz, 9MHz, and 9MHz base timer output.

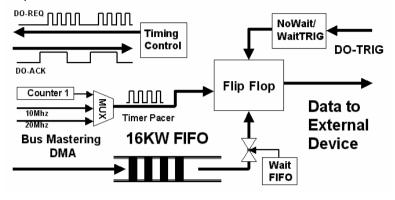

# 4.8 Starting Mode

Users can also control the starting mode of digital input and output by external signals (DITRIG and DOTRIG) with the software programs. The trigger modes includes NoWait, WaitTRIG, WaitFIFO, and WaitBoth.

NoWait: The data transfer is started immediately when a I/O transfer command is issued.

- 2. **WaitTRIG:** The data transfer will not start until external trigger signal (DI-TRIG for digital input, DO-TRIG for digital output) is activated.

- 3. WaitFIFO: This starting mode is only available for digital output. The data transfer is started until the output FIFO is not almost empty. The threshold of FIFO almost empty is software programmable.

- 4. WaitBoth: This starting mode is only available for digital output. The data transfer is started until the output FIFO is not almost empty and DO-TRIG signal is activated.

The software driver functions of 5.6 and 5.7 are provided to setup the starting mode of digital input and digital output, respectively.

### 4.9 Active Terminator

For cPCI/PCI-7300A, it is important to terminate your cable properly to reduce or eliminate signal reflections in the cable. The PCI-7300A support active terminator on board, you can enable or disable the terminator by software selection (Please refer to section 5.5 function 7300 config).

The active terminator is the same as the one used in SCSI 2. When the terminator is ON, it presents a terminal 110-ohm impedance to the transmission line to match the line impedance. When it is OFF, it just add a few pF capacitance to the line

# 4.10 Digital Input Operation Mode

# 4.10.1 Digital Input DMA in Internal Clock Mode

There are three sources to trigger digital input in the internal clock mode: 20MHz, 10MHz, and programmable timer 82C54. There are three counters in 82C54, where the counter 0 is used for sampling clock source for digital input. The operations sequence of digital input with internal clock are listed as follows:

- 1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

- 2. Enable or disable the active terminators.

- 3. Define the input sampling rate to be 20MHz, 10MHz, or the output of 82C54 counter 0.

- 4. Define the starting mode to be NoWait or WaitTRIG.

- 5. The digital input data are stored in the input FIFO after a DI command is issued and waiting for DI-TRIG signal if in WaitTRIG mode.

- 6. The data in the input FIFO will be transferred into system memory directly and automatically by bus mastering DMA.

The operation flow is show as below:

Notes: When the DMA function of digital input starts, the input data will be stored in the FIFO of the cPCI/PCI-7300A. The data then transfer to system memory if PCI bus is available. If the speed of translation from external device to the FIFO on board is higher than that from FIFO to system memory or the PCI bus is busy for a long time, the FIFO become full and overrun situation occurs after the next data being written to the input FIFO. Users should check the overrun status to see whether the overrun occurs or not. Some input data will lost when the input FIFO is overrun.

Notes: The overrun occurs when the DMA idle time (from the end of DMA transfer N to the start of DMA transfer N+1) is longer than the on-board FIFO buffer time. The FIFO size is 16K sample, so it has 1.6 ms buffer time for 10MHz sampling rate if the FIFO is empty when last DMA is complete. Users may try different DMA buffer size to see how the DMA buffer size affects the overall performance. Generally, the larger DMA size the less overhead, however, the process time required between DMAs also increases.

# 4.10.2 Digital Input DMA in External Clock Mode

The digital input data transfer can be controlled by external strobe, which is from pin-83 DI-REQ of CN1. The operation sequence is very similar to Internal Clock. The only difference is the clock source comes from the outside peripheral devices. The operations sequence of digital input with external clock are listed:

- 1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

- 2. Enable or disable the active terminators.

- 3. Define the input sampling rate as external clock. Connect the external clock to the input pin DI-REQ.

- 4. Define the starting mode to be NoWait or WaitTRIG.

- 5. The digital input data are stored in the input FIFO after a DI command is issued and waiting for DI-TRIG signal if in WaitTRIG mode..

- 6. The data saved in FIFO will transfer to system memory of your computer directly and automatically by bus mastering DMA.

- 7. The DI-ACK signal indicates the status of the cPCI/PCI-7300A's input FIFO is in external clock mode. When the digital input circuit of cPCI/PCI-7300A is enabled and its FIFO is not almost full, the DIACK signal will remain asserted. If the external device does not transfer data according to the status of DI-ACK, the on-board FIFO could be full and data could be lost.

The operation flow is show as below:

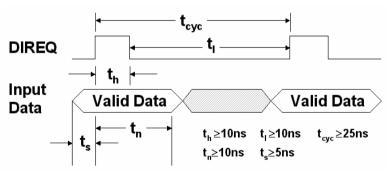

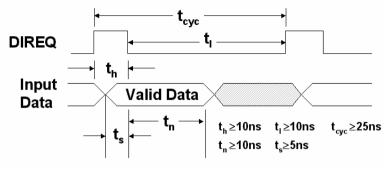

The followings are timing diagrams of the DI-REQ and the input data. The active edge of DI-REQ can be programmed by the function 5.5.

DIREQ as input data strobe (when Rising Edge Active)

DIREQ as input data strobe (when Falling Edge Active)

Notes: From the timing diagram of external clock mode, the maximum frequency can be up to 40MHz. However, users should note that when the sampling frequency of digital input is higher than the PCI bus bandwidth (33Mhz), or the bandwidth of chipset (30Mhz typically) from PCI bus to system memory. Users should check the overrun status when the DMA block size is larger than 16K samples. If overrun always happens, users should reduce the DMA block size or slow down the sampling frequency. For example, the DMA block size should be smaller than 64K when the external clock is 40Mhz in the DOS Operation

# 4.10.3 Digital Input DMA in Handshaking Mode

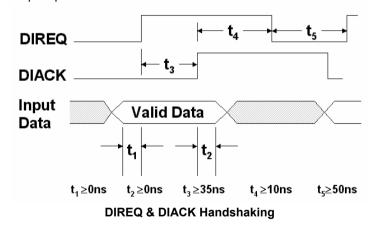

For digital input, through DI-REQ input signal and DI-ACK output signal, the digital input can have simple handshaking data transfer. The operations sequence of digital input with handshaking are listed:

- 1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

- Enable or disable the active terminators.

- Define the input sampling rate as handshaking mode. Connect the handshaking signals of the external device to input pin DI-REQ and output pin DI-ACK.

- 4. Define the starting mode to be NoWait or WaitTRIG.

- 5. After digital input data is ready on device side, the peripheral device strobe data into the cPCI/PCI-7300A by asserting a DIREQ signal,

- The DIREQ signal caused the PCI-7300A to latch digital input data and store it into FIFO

- 7. The PCI-7300A asserts a DIACK signal when it is ready for another input, the step 5 to step 7 will be repeated again.

8. The data saved in FIFO will transfer to system memory of your computer directly and automatically by bus mastering DMA.

The operation flow is show as below:

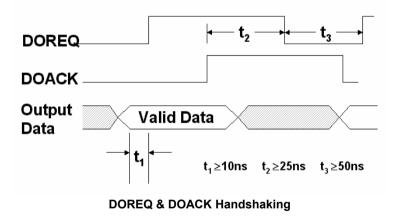

The following figure shows the timing requirement of the handshaking mode digital input operation.

Note: DIREQ must be asserted until DIACK asserts, DIACK will be asserted until DIREQ de-asserted.

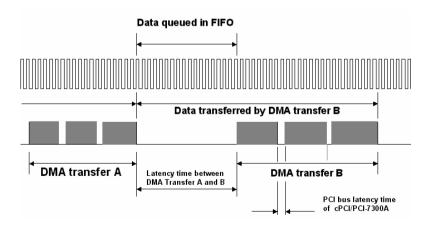

# 4.10.4 Continuous Digital Input

If the digital input operation still active after the competition of the previous DMA transfer and do not clear the data in the input FIFO when the next DMA starts, the cPCI/PCI-7300A can achieve the continuous digital input function in a high-speed sampling rate. In this case, the input FIFO buffers the input data and waits for the next DMA to move the queued data to the system memory. To avoid the overrun of input FIFO causes the data lost of the continuous digital input, the latency time of the next DMA should be smaller than the time to overrun the input FIFO. There are some rules of thumb should be mentioned here:

- 1. The lower the sampling frequency is, the longer the time to overrun the input FIFO is. That means the fewer overrun situations will occur.

- To reduce the latency time between two DMA transfers, please disable unnecessary PCI bus mastering devices, and remove the unnecessary processes in your application programs.

- When high-speed sampling frequency is applied, the larger block size will improve the efficiency of DMA transferring, and probability of overrun in the DMA process will be reduced.

- 4. To apply the high-speed continuous digital input, it is recommended to execute your application programs in the non-multitask operation system to reduce the latency time between two DMA transfers.

Notes: The latency time between two DMA transfers is different from the PCI bus latency time mentioned in the previous section of "Bus Mastering". The former means the time difference between two continuous DMA processes started by the software. And the latter means the time difference between two continuously hardware DMA requests on the PCI bus within a DMA process.

# 4.11 Digital Output Operation Mode

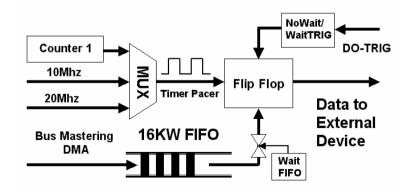

# 4.11.1 Digital Output DMA in Internal Clock Mode

There are three sources to trigger digital output: 20MHz, 10MHz, and programmable timer 82C54. There are three counters in 82C54, where the counter 1 is used timer pacer for digital output. The operations sequence of digital output with internal clock are listed:

- 1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

- 2. Enable or disable the active terminators.

- 3. Define the output timer pacer rate to be 20MHz, 10MHz, or the output 82C54 timer 1. The timer pacer controls the output rate.

- 4. Define the starting mode to be NoWait, WaitTRIG, WaitFIFO, or WaitBoth

- 5. The output data saved in the system memory will be transferred to output FIFO directly and automatically by bus mastering DMA.

- The digital output data will be transferred to the external device after a DO command is issued and DO-TRIG signal is activated.

The operation flow is show as below:

As the data output in the internal clock mode, the DOREQ signal could be use as the output strobe to indicate the output operation to the external device. The timing diagram of the DOREQ is shown as follows:

DOREQ as output data strobe

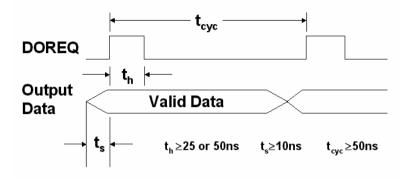

# 4.11.2 Digital Output DMA in Handshaking Mode

For digital output, through DO-REQ output signal and DO-ACK input signal, the digital output can have simple handshaking data transfer.

The operations sequence of digital output in handshaking mode are listed:

- 1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

- Enable or disable the active terminators.

- Define the output clock mode as handshaking mode. Connect the handshaking signals of the external device to output pin DO-REQ and input pin DO-ACK.

- 4. Define the starting mode to be NoWait, WaitTRIG, WaitFIFO, or WaitBoth

- 5. Digital output data is moved from PC's system memory to output FIFO by using bus mastering DMA.

- After output data is ready. A DO-REQ signal is generated and sent the output data to the external device.

- 7. After a DO-ACK signal is gotten, the step 6 and step 7 will be repeated again

The operation flow is show as below:

The timing diagram of the DOREQ and DOACK in the DO handshaking mode is shown as follows:

Note: DOACK must be deserted before DOREQ asserts, DOACK can be asserted any time after DOREQ asserts, DOREQ will be reasserted after DOACK is asserted.

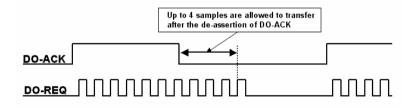

# 4.11.3 Digital Output DMA in Burst Handshaking Mode

The burst handshaking mode is a fast and reliable data transfer protocol. It has both advantage of handshaking mode, which is reliable, and the advantage of internal clock mode, which is fast. When using this mode, the sender has to check the availability of receiver indicated by the DO-ACK signal before it starts to send data. Once the DO-ACK is asserted, the receiver has to keep the DO-ACK signal asserted before its input buffer becomes too small. When the DO-ACK is de-asserted, indicating the receiver's buffer has not much space for new data, the sender is still allowed to send 4 data to the receiver, and the receiver has to receive these data. The following figure illustrates the operation of the burst handshaking mode:

The operations sequence of digital output in burst handshaking mode are listed:

- 1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

- Enable or disable the active terminators.

- 3. Define the output clock as burst handshaking mode and decide the timer pacer rate to be 20Mhz, 10Mhz, or the output of 82C54 timer 1.

- Connect the handshaking signals of the external device to output pin DO-REQ and input pin DO-ACK.

- 5. Define the starting mode to be NoWait, TrigWait, WaitFIFO, or WaitBoth

- 6. Digital output data is moved from PC's system memory to output FIFO by using bus mastering DMA.

- 7. After output data is ready. DO-REQ signals are generated and sent the output data to the external device when the DO-ACK is asserted.

The operation flow is show as below:

Notes: When the DMA function of digital output starts, the output data will transfer to the output FIFO of cPCI/PCI-7300A when PCI bus is available. If the speed of translation from the FIFO on board to the external device is higher than that from system memory to the output FIFO or the PCI bus is busy for a long time, the FIFO become empty and under-run situation occurs after the next data being read from the output FIFO. Users should check the under-run status to see whether the under-run occurs or not. Some output data will repeat when the output FIFO is under-run.

Notes: To avoid the under-run of output FIFO when digital output starts and PCI bus is still busy, it is highly recommended to set the starting mode to be WaitFIFO. The higher the timer pacer rate is the larger amount of almost empty threshold should be set to prevent the under-run situation.

#### 4.11.4 Pattern Generator

The digital data is output to the peripheral device periodically based on the clock signals occur at a constant rate. The digital pattern are stored in the cPCI/PCI-7300A's on-board FIFO with the length of pattern less than or equal to 16K samples.

The operations sequence of pattern generator are listed:

- 1. Define the input configuration to be 32-bit, 16-bit or 8-bit data width.

- 2. Enable or disable the active terminators.

- 3. Define the output timer pacer rate to be 20MHz, 10MHz, or the output 82C54 timer 1. The timer pacer controls the output rate.

- 4. Set the output patterns into the output FIFO by direct FIFO access

- 5. Start the pattern generator function.

- 6. The pattern generator function will not stop until users stop the process

# 4.12 Auxiliary DIO

The cPCI/PCI-7300A also includes four auxiliary digital inputs and four digital outputs, which can be applied to achieve the simple I/O functions. Users can refer to the functions 5.8 ~5.11 for the detailed information.

# C/C++ Libraries

This chapter describes the software library for operating this card. Only the functions in DOS library and Windows 95 DLL are described. Please refer to the PCIS-DASK function reference manual, which included in ADLINK CD, for the descriptions of the Windows 98/NT/2000 DLL functions.

The function prototypes and some useful constants are defined in the header files LIB directory (DOS) and INCLUDE directory (Windows 95). For Windows 95 DLL, the developing environment can be Visual Basic 4.0 or above, Visual C/C++ 4.0 or above, Borland C++ 5.0 or above, Borland Delphi 2.x (32-bit) or above, or any Windows programming language that allows calls to a DLL. It provides the C/C++, VB, and Delphi include files.

#### 5.1 Libraries Installation

Please refer to the "**Software Installation Guide**" for the detail information about how to install the software libraries for DOS, or Windows 95 DLL, or PCIS-DASK for Windows 98/NT/2000.

The device drivers and DLL functions of Windows 98/NT/2000 are included in the PCIS-DASK. Please refer the PCIS-DASK user's guide and function reference, which included in the ADLINK CD, for detailed programming information.

# 5.2 Programming Guide

# 5.2.1 Naming Convention

The functions of the NuDAQ PCI cards or NuIPC CompactPCI cards' software driver are using full-names to represent the functions' real meaning. The naming convention rules are:

#### In DOS Environment:

\_{hardware\_model}\_{action\_name}. e.g. \_7300\_Initial().

All functions in PCI-7300A driver are with 7300 as {hardware\_model}. But they can be used by PCI-7300A, cPCI-7300.

In order to recognize the difference between DOS library and Windows 95 library, a capital "W" is put on the head of each function name of the Windows 95 DLL driver. e.g. w 7300 Initial().

# 5.2.2 Data Types

We defined some data type in Pci\_7300.h (DOS) and Acl\_pci.h (Windows 95). These data types are used by NuDAQ Cards' library. We suggest you to use these data types in your application programs. The following table shows the data type names and their range.

| Type Name | Description                    | Range                       |  |