# PXI-9820

# 2-CH 65 MS/s 14-Bit Digitizer with SDRAM

## **Features**

- PXI specifications Rev. 2.1 compliant

- 3U Eurocard form factor, CompactPCI compliant (PICMG2.0 R3.0)

- 14-bit A/D resolution

- Up to 60 MS/s sampling rate per channel with internal timebase

- Up to 65 MS/s sampling rate per channel with external timebase

- Up to 130 MS/s sampling rate in "ping pong" mode

- 2-CH single-ended bipolar inputs

- >30 MHz -3dB bandwidth

- Up to 512 MB on-board SODIMM SDRAM

- Programmable ranges of ±1 V and ±5 V

- User-selectable input impedance of 50  $\Omega$  or high input impedance

- Scatter-gather DMA

- Analog and digital triggering

- 2-CH synchronous digital inputs

- Fully auto calibration

- Multiple modules synchronization through PXI trigger bus

- **Operating Systems**

- Windows 98/NT/2000/XP/2003

- Linux

- Recommended Software

- VB/VC++/BCB/Delphi

- DAQBench

- Driver Support

- DAQ-LVIEW PnP for LabVIEW

- DAQ-MTLB for MATLAB

- DAQBOY for Windows

- WD-DASK for Linux

- WD-DASK/X for Windows

# Introduction

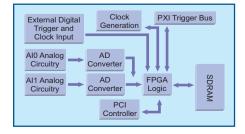

ADLINK PXI-9820 is a 65 MS/s, high-resolution PXI digitizer with deep SODIMM SDRAM memory. The device features flexible input configurations, including programmable input ranges and user-selectable input impedance. With the deep on-board acquisition memory, the PXI-9820 is not limited by the 132 MB/s bandwidth of PCI bus and can record the waveform for a long period of time. The PXI-9820 is ideal for high-speed waveform capturing, such as radar and ultrasound applications, as well as software radio applications, or those signal digitizing applications which need deep memory for data storage.

# Analog Input

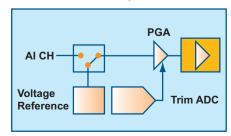

The PXI-9820 device features two analog input channels. The small signal bandwidth of each channel exceeds 30 MHz. The input ranges are programmable as either  $\pm 5$  V or  $\pm 1$  V. The 14-bit A/D resolution makes the PXI-9820 ideal both for time-domain and frequency-domain applications.

# **Acquisition System**

ADLINK PXI-9820 device uses a pair of 65 MS/s, 14-bit pipeline ADCs to digitize the input signals, and the device provides an internal 60 MHz timebase for data acquisition. The maximum real-time sampling rate is 60 MS/s with internal timebase, and is up to 65 MS/s with external timebase. By using the "ping pong" mode, the sampling rate is up to 120 MS/s with internal timebase or 130 MS/s with external timebase.

# Acquisition Memory

The PXI-9820 device supports different size of SODIMM SDRAM ranging from 128 MB to 512 MB.

The digitized data are stored in the on-board SDRAM before being transferred to the host memory. The PXI-9820 device uses the scatter-gather bus mastering DMA to move data to the host memory. If the data throughput from the PXI-9820 is less than the available PCI bus bandwidth, the PXI-9820 also features on-board 3k-sample FIFO to achieve real-time transfer bypassing the SDRAM, directly to the host memory.

# Triggering

Thanks to PXI versatile trigger functions, the PXI-9820 device features flexible triggering functionalities, such as analog and digital triggering. The analog trigger features programmable trigger thresholds on rising or falling edges on both input channels. The 5 V/TTL digital trigger comes from PXI trigger bus or the external SMB connector for synchronizing multiple devices.

Post-trigger, pre-trigger, delay-trigger and middletrigger modes are available to acquire data around the trigger event. The PXI-9820 also features repeated trigger acquisition, so you can acquire data in multiple segments coming with successive trigger events at extremely short rearming interval.

# Multiple-Instrument Synchronization

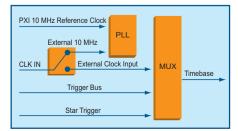

The PXI-9820 implements star trigger and trigger bus to route timing and trigger signals between one or more PXI-9820 and other PXI modules. These interfaces allow users to synchronize multiple PXI modules into a system easily. Timebase is also selectable. Users could choose using internal clock or the output of the onboard PLL with the reference

clock from external clock input or PXI 10 MHz reference clock.

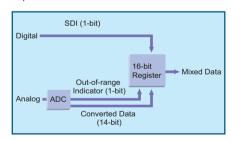

# Synchronous Digital Inputs

SDI (synchronous digital input) is the digital input synchronously sampled with analog input. The digital inputs are latched right with the clock edge while the analog signals are sampled, and the digital input combining the 14-bit analog data are stored into SDRAM. This functions is ideal for mixed signal acquisition.

## **Calibration**

The auto-calibration function of the PXI-9820 is performed with trim DACs to calibrate the offset and gain errors of the analog input channels. Once the calibration process is done, the calibration constant will be stored in EEPROM such that these values can be loaded and used as needed by the board. Because all the calibration is conducted automatically by software commands, users don't have to adjust trimpots to calibrate the modules manually.

# **Specifications**

# Analog Input

- Number of channels: 2 simultaneous-sampled single-ended

- Resolution: 14 bits

- Maximum sampling rate

- 65 MS/s for 2 inputs

- 130 MS/s for Ping-Pong mode

- On-board sample memory

- 128 MB. standard

- up to 512 MB, optional

- Bandwidth (-3 dB): 30 MHz minimum

- Input signal ranges: (software programmable)

- Input Coupling: DC

- Overvoltage protection

| Range | Overvoltage protection |

|-------|------------------------|

| ± 5 V | ± 14 V                 |

| ± 1 V | ± 5 V                  |

- Input Impedance (soldering selectable):  $50\Omega$ ,  $1.5 M\Omega$

- Crosstalk: < -80 dB, DC to 1MHz

- Total harmonic distortion (THD): -75 dB

- Signal-to-Noise ratio (SNR)

| Range | SNR   |

|-------|-------|

| ± 5 V | 66 dB |

| ± 1 V | 62 dB |

- Spurious-free dynamic range (SFDR): 75 dB

- Data transfer:

bus mastering DMA with scatter-gather

# **Auto Calibration**

- On-board reference: +5 V

- Temperature drift: 2 ppm/°C

- Stability: 6 ppm/1000 Hrs **External Timebase Input**

- Selectable as 10 MHz input for PLL or direct external timebase input

- Connector: SMB

- Impedance: 50Ω Coupling: AC

- Input amplitude: 1 V<sub>pp</sub> to 2 V<sub>pp</sub>

- Overvoltage protection: 2.5 Vpp

- Frequency range: 500 kHz 65 MHz

# **Triggering**

- Analog triggering

- Modes:

pre-trigger, post-trigger, middle-trigger, delay-trigger

- Source: CH0 and CH1

- Slope: rising/falling

- Coupling: DC

- Trigger sensitivity:

256 steps in full-scale voltage range

- Digital triggering

- Modes:

pre-trigger, post-trigger, middle-trigger, delay-trigger

- · Source: external digital trigger from SMB

- Slope: rising/falling

- Compatibility: 5 V/TTL

- Minimum pulse width: 10 ns

- Repeated trigger rearming interval: 2 cycles of timebase

- Pre-trigger depth:

128 MB or 512 MB, depending on memory option

■ Post-trigger depth:

128 MB or 512 MB, depending on memory option

# **Synchronous Digital Input**

- Number of channels: 2

- Compatibility: 5 V/TTL

- Data transer: bus mastering DMA with scatter/gather

## **General Specifications**

- I/O connector

- BNC x 2 for analog inputs

- SMB x 4 for external digital trigger, external time base, and synchronous digital inputs

- Operating temperature: 0 to 50°C

- Storage temperature: -20 to 80°C

- Relative humidity: 5 to 95%, noncondensing

- Power requirements

| Power Rail | Current                                                  |

|------------|----------------------------------------------------------|

| 5 V        | 900 mA                                                   |

| 12 V       | 305 mA                                                   |

| 3.3 V      | 360 mA (with 128 MB SDRAM)<br>500 mA (with 512 MB SDRAM) |

■ Dimensions (not including connectors) 160 mm x 100 mm

#### Certificate

■ EMC/EMI: CE, FCC Class A

#### **Accessories**

- SMB-SMB-1M

- 1-meter SMB to SMB cable

- SMB-BNC-1M

1-meter SMB to BNC cable

SMB-SMB-1M

SMB-BNC-1M

# **Ordering Information**

- PXI-9820D/128 2-CH 65 MS/s 14-Bit Digitizer with 128 MB Memory

- PXI-9820D/5122-CH 65 MS/s 14-Bit Digitizer with 512 MB